Itanium

Itanium-based systems were produced by HP and its successor Hewlett Packard Enterprise (HPE) as the Integrity Servers line, and by several other manufacturers.[c] HP hired Bob Rau of Cydrome and Josh Fisher of Multiflow, the pioneers of very long instruction word (VLIW) computing.[13][14] In 1993 HP held an internal competition to design the best (simulated) microarchitectures of a RISC and an EPIC type, led by Jerry Huck and Rajiv Gupta respectively.[21] At the meeting with HP, Intel's engineers were impressed when Jerry Huck and Rajiv Gupta presented the PA-WideWord architecture they had designed to replace PA-RISC."When we saw WideWord, we saw a lot of things we had only been looking at doing, already in their full glory", said Intel's John Crawford, who in 1994 became the chief architect of Merced, and who had earlier argued against extending the x86 with P7.In June 1994 Intel and HP announced their joint effort to make a new ISA that would adopt ideas of Wide Word and VLIW.[22] The expectations for Merced waned over time as delays and performance deficiencies emerged, shifting the focus and onus for success onto the HP-led second Itanium design, codenamed McKinley.[37] Later it was reported that HP's motivation when starting to design McKinley in 1996 was to have more control over the project so as to avoid the issues affecting Merced's performance and schedule.[50] During development, Intel, HP, and industry analysts predicted that IA-64 would dominate first in 64-bit servers and workstations, then expand to the lower-end servers, supplanting Xeon, and finally penetrate into the personal computers, eventually to supplant RISC and complex instruction set computing (CISC) architectures for all general-purpose applications, though not replacing x86 "for the foreseeable future" according to Intel.[60] Several groups ported operating systems for the architecture, including Microsoft Windows, OpenVMS, Linux, HP-UX, Solaris,[61][62][63] Tru64 UNIX,[60] and Monterey/64.[65] Within hours, the name Itanic had been coined on a Usenet newsgroup, a reference to the RMS Titanic, the "unsinkable" ocean liner that sank on her maiden voyage in 1912.After having sampled 40,000 chips to the partners, Intel launched Itanium on May 29, 2001, with first OEM systems from HP, IBM and Dell shipping to customers in June.[75] POWER and SPARC remained strong, while the 32-bit x86 architecture continued to grow into the enterprise space, building on the economies of scale fueled by its enormous installed base.Only a few thousand systems using the original Merced Itanium processor were sold, due to relatively poor performance, high cost and limited software availability.Few of the microarchitectural features of Merced would be carried over to all the subsequent Itanium designs, including the 16+16 KB L1 cache size and the 6-wide (two-bundle) instruction decoding.McKinley also greatly increases the number of possible instruction combinations in a VLIW-bundle and reaches 25% higher frequency, despite having only eight pipeline stages versus Merced's ten.Under the influence of Microsoft, Intel responded by implementing AMD's x86-64 instruction set architecture instead of IA-64 in its Xeon microprocessors in 2004, resulting in a new industry-wide de facto standard.[91][92] After a delay to "mid-2006" and reduction of the frequency to 1.6 GHz,[93] on July 18 Intel delivered Montecito (marketed as the Itanium 2 9000 series), a dual-core processor with a switch-on-event multithreading and split 256 KB + 1 MB L2 caches that roughly doubled the performance and decreased the energy consumption by about 20 percent.[111] The device uses a 65 nm process, includes two to four cores, up to 24 MB on-die caches, Hyper-Threading technology and integrated memory controllers.[132][133][134] On 31 January 2013 Intel issued an update to their plans for Kittson: it would have the same LGA1248 socket and 32 nm process as Poulson, thus effectively halting any further development of Itanium processors.[137] Even Hewlett-Packard, the main proponent and customer for Itanium, began selling x86-based Superdome and NonStop servers, and started to treat the Itanium-based versions as legacy products.[155] Before "Tukwila" moved away from the FSB, chipsets supporting such technologies were manufactured by all Itanium server vendors, such as HP, Fujitsu, SGI, NEC, and Hitachi.Two E8870 can be linked together by two E8870SP Scalability Port Switches, each containing a 1MB (~200,000 cache lines) snoop filter, to create an 8-socket system with double the memory and PCI-X capacity, but still only one ICH4.The memory is of HP's custom design, using the DDR2 protocol, but twice as tall as the standard modules and with redundant address and control signal contacts.[175][176][177][178] SGI's second-generation SHUB 2.0 chipset supported up to 48 GB of DDR2 memory, 667 MT/s FSB, and could connect to I/O modules providing PCI Express.Similarly, HP implemented a method to execute PA-RISC/HP-UX on the Itanium/HP-UX via emulation, to simplify migration of its PA-RISC customers to the radically different Itanium instruction set.[213] An October 2008 Gartner report on the Tukwila processor stated that "...the future roadmap for Itanium looks as strong as that of any RISC peer like Power or SPARC.[220] Itanium failed to make significant inroads against IA-32 or RISC, and suffered further following the arrival of x86-64 systems which offered greater compatibility with older x86 applications.In a 2009 article on the history of the processor — "How the Itanium Killed the Computer Industry" — journalist John C. Dvorak reported "This continues to be one of the great fiascos of the last 50 years".In June 2016, Hewlett Packard Enterprise (the corporate successor to HP's server business) was awarded $3 billion in damages from the lawsuit.

processors in the TOP500 ranking list of supercomputers (1993–2019)

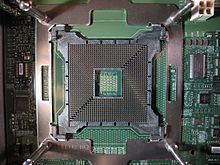

clock ratemission critical serversHigh performance computingTechnology nodeMicroarchitectureInstruction setMemory (RAM)Flip-chipland grid arrayPAC 418PAC 611LGA 124864-bitmicroprocessorsIntel Itanium architectureHewlett-Packardenterprise servershigh-performance computingpersonal computersreduced instruction set computingcomplex instruction set computingHewlett Packard EnterpriseIntegrity Serversenterprise-class systemsx86-64Power ISAOpteronreduced instruction set computerinstructions per cycledependencyexception handlingBob RauCydromeJosh FisherMultiflowvery long instruction wordinstructionscompilervalid combinations of instructions that can be executed at the same timesuperscalar processorsExplicitly Parallel Instruction Computingissue widthpredicationbranchesdelay slotsexecution unitsPA-RISCRajiv GuptaParagonJohn CrawfordPowerPCHP LabsEE Timesa floating-point hardware bugPentiumfloorplanned180 nm250 nmtaped out180 nm processMicroprocessor ReportFred PollackPA-8000tape-outsteppingAndy GroveCompaqSilicon GraphicsMicrosoft WindowsOpenVMSSolarisTru64 UNIXMonterey/64UsenetRMS Titanicocean linerThe RegisterPAC418IBM POWERSun Microsystems32-bit130 nmPAC611Fort Collins, Coloradotaping outinstruction set architectureheat spreaderremovedMontecito (processor)POWER4hyper-threadingdual-coreFoxton Technology65 nm processfront-side buslockstepLGA1248Tukwila (processor)DEC Alphafour processor coresCommon System Interfacedouble-device data correctionIntel QuickPath InterconnectNehalemBeckton32 nm45 nmHot ChipsIntel Instruction ReplayLGA2011SuperdomeNonStopGartner Inc.IntegrityProLiantSystem xPowerEdgeHitachiUnisysES7000FujitsuInspurHuaweisystem integratorsWindowsSpectre